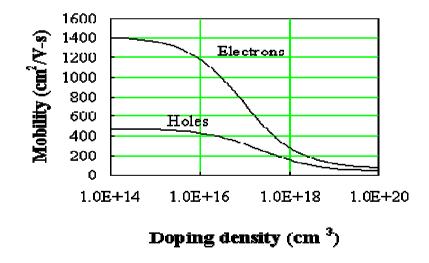

# SEMICONDUTTORI ESTRINSECI: EFFETTO SULLA MOBILITÀ

Anche le mobilità di elettroni e lacune sono influenzate dal drogaggio

## SEMICONDUTTORI ESTRINSECI: CONDUCIBILITÀ ELETTRICA

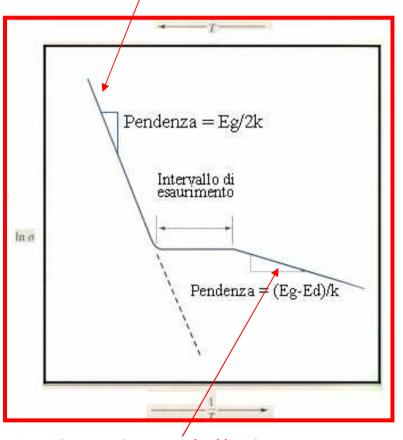

Comportamento intrinseco

- A temperatura ambiente per avere silicio drogato con arsenico dentro l' intervallo di esaurimento: 10<sup>21</sup> atomi As/m<sup>3</sup>.

- Nei semiconduttori di tipo-p si parla di intervallo di saturazione.

- È importante osservare gli i semiconduttori devono operare in tali intervalli in modo che σ sia poco variabile con T.

Ionizzazione delle impurezze

## SEMICONDUTTORI ESTRINSECI:

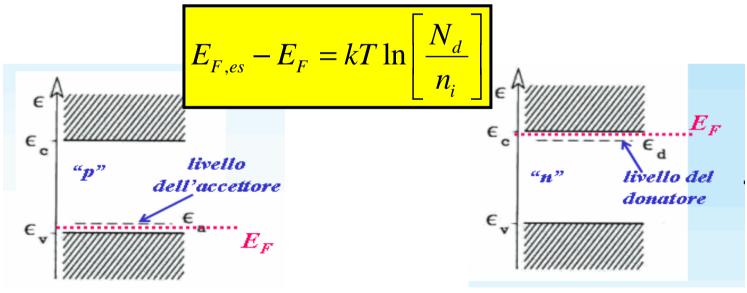

Nei semiconduttori estrinseci il livello di Fermi ( $E_{F,es}$ ) si sposta verso l'alto per quelli di tipo-n e verso il basso per quelli di tipo-p.

Nell'ipotesi che l'approssimazione  $E_C - E_{F,es} \gg kT$  sia conservata la posizione del livello di Fermi per semiconduttore estrinseco di tipo-n si può determinare da:

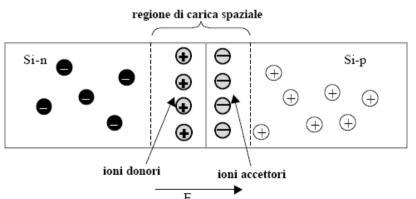

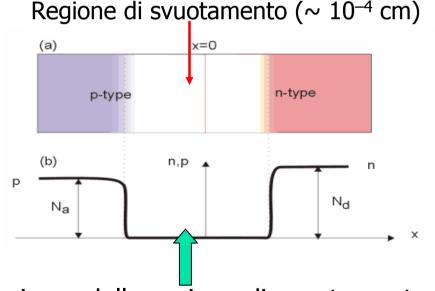

### GIUNZIONE p-n

Giunzione p-n: pezzo di semiconduttore tipo-n unito ad un pezzo di semiconduttore di tipo-p (in realtà si prepara per diffusione allo stato solido di droganti tipo-p su un semiconduttore di tipo-n).

Le proprietà elettriche della giunzione p-n sono alla base di tutti i dispositivi basati sui semiconduttori.

Ampiezza della regione di svuotamento inversamente proporzionale al drogaggio

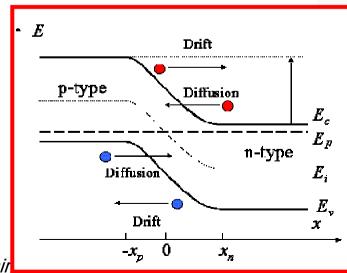

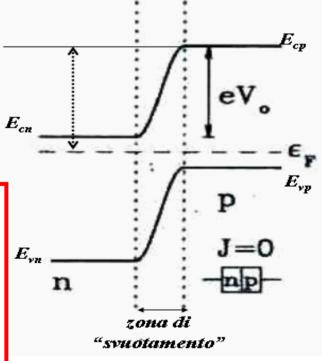

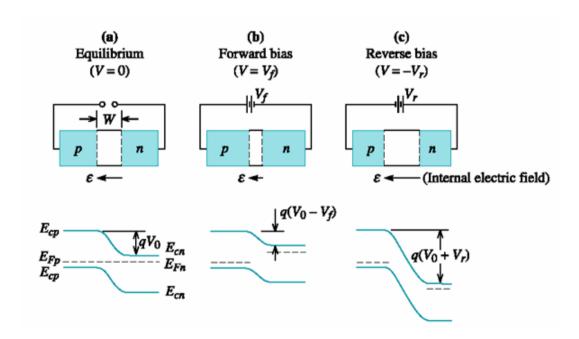

## GIUNZIONE p-n: EQUILIBRIO TERMICO

Non c'è tensione applicata ai capi della giunzione.

Flusso di elettroni e lacune fino al raggiungimento dell'equilibrio:

i livelli di Fermi delle due regioni si allineano

*Flettrici* – L15

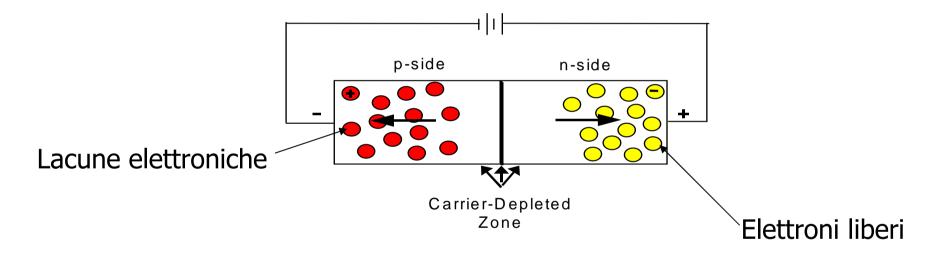

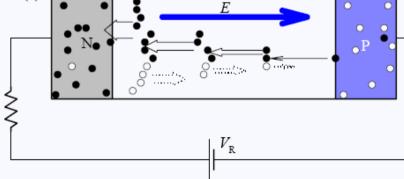

### GIUNZIONE p-n: POLARIZZAZIONE INVERSA

Collegando gli estremi della giunzione ad una batteria come in figura:

In ciascun lato della giunzione i portatori di maggioranza sono allontanati dalla giunzione stessa. Lungo la giunzione può circolare solo una debolissima corrente, legata ai portatori di minoranza, praticamente indipendente dalla tensione V applicata (corrente di dispersione ~ μA).

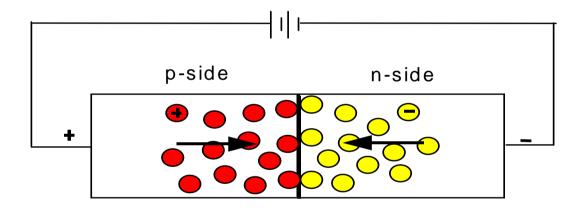

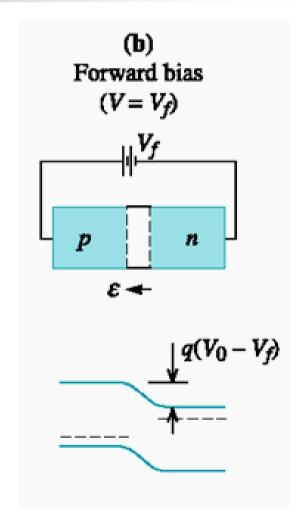

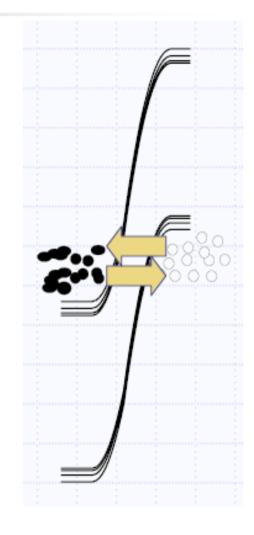

## GIUNZIONE p-n: POLARIZZAZIONE DIRETTA

Collegando gli estremi della giunzione ad una batteria come in figura:

In ciascun lato della giunzione i portatori di maggioranza sono spinti verso la giunzione. Lungo la giunzione circola una elevata corrente, legata ai portatori di maggioranza, che dipende dalla tensione V applicata.

## GIUNZIONE p-n: MODIFICA DEI DIAGRAMMI A BANDE ENERGETICHE

I diagrammi a bande energetiche si modificano per conformarsi alla condizione di equilibrio termico.

## GIUNZIONE p-n: CALCOLO DELLA CORRENTE CIRCOLANTE

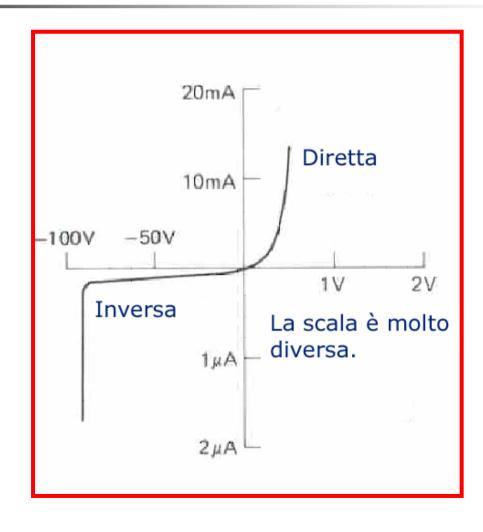

Si può dimostrare che la corrente circolante in una giunzione polarizzata è data dalla seguente equazione (di Shockley):

$$I = I_0 \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right]$$

I<sub>0</sub> è la corrente di dispersione

## GIUNZIONE p-n: CURVA CARATTERISTICA I-V

## GIUNZIONE p-n: MECCANISMI SCARICA

- Meccanismi di rottura (breakdown) della giunzione quando la polarizzazione inversa oltrepassa una certa soglia:

- a) breakdown per effetto valanga (avalanche breakdown)

- b) breakdown per effetto Zener (Zener breakdown)

- EFFETTO VALANGA: per campi elettrici molto elevati gli  $e^-$  hanno energia cinetica superiore a  $E_g$ ; diventa probabile che urti tra questi  $e^-$  e il reticolo diano luogo alla formazione di coppie lacune-elettroni, le quali a loro volta danno urti in grado di generare altre coppie di portatori con un fenomeno di moltiplicazione a valanga. Ogni materiale è caratterizzato da un valore soglia di campo oltre il quale ha luogo

l'effetto valanga.

## GIUNZIONE p-n: MECCANISMI SCARICA

**EFFETTO ZENER:** quando la zona di svuotamento è sottile è possibile che gli elettroni attraversino la giunzione per effetto tunnel tra gli elettroni della BV (zona p) e la BC (zona n) (fenomeno quantistico): sono rotti i legami covalenti dal campo elettrico. Il fenomeno è favorito da una zona di svuotamento sottile (drogaggio pesante). Tranne drogaggi molto forti il campo di rottura per effetto valanga è inferiore a quello Zener.

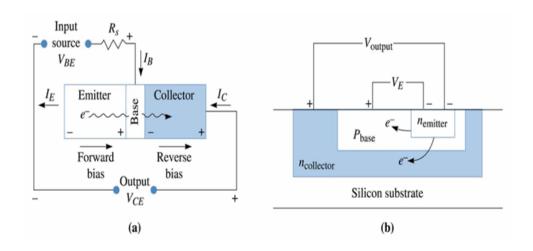

# APPLICAZIONI DELLE GIUNZIONI p-n

La giunzione p-n è alla base dei componenti elettronici fondamentali quali transistor, MOSFET, diodi, ecc.

### MATERIALI PER SEMICONDUTTORI

- I materiali

potenzialmente

utilizzabili come

semiconduttori sono

molteplici:

- Si, Ge elementi

- GaAs, InP, InSb come composti III-V

- CdTe, ZnS come composti II-VI

### MATERIALI PER SEMICONDUTTORI

- Cosa ha dettato il successo del silicio come materiale principe per l'elettronica? Due caratteristiche non del Si, ma del suo ossido SiO<sub>2</sub>:

- L'ossido di silicio (SiO<sub>2</sub>) risulta praticamente impermeabile alle impurezze utili al drogaggio del silicio (maschera).

- L'ossido può essere rimosso con acido fluoridrico (HF) a cui invece è inerte il silicio (selettività dell'attacco chimico).

Diffusione del silicio sulla crosta terrestre: 27.7 % (secondo solo ad O)

Minerali più importanti: silicati (di moltissimi tipi differenti), quarziti e sabbia (gli ultimi due sono a base di silice SiO<sub>2</sub>). La silice è la materia prima per la preparazione del silicio purissimo.

Caratteristiche principali del silicio:

Simbolo Si, Z = 14, PA = 28.086

Solido covalente con struttura cristallina tipo diamante, a = 0.543 nm (N  $\approx 5x10^{28}$  atomi/m<sup>3</sup>)

Densità 2.33 g/cm<sup>3</sup>,  $T_f = 1410$  °C

La tecnologia del silicio rappresenta il punto più sofisticato e complesso di applicazione della tecnologia dei materiali al mondo d'oggi.

Le caratteristiche elettriche dei dispositivi sono fortemente influenzate da:

- impurezze presenti (un drogaggio di 10<sup>21</sup> atomi As/m<sup>3</sup> equivale a circa 100 ppm)

- dislocazioni presenti

- eventuale bordo grano

- ⇒ Il silicio dei semiconduttori deve essere purissimo, con reticolo perfetto e monocristallino

Il ciclo tecnologico è molto complesso e coinvolge processi e apparecchiature di costi ingenti. Sono innumerevoli i prodotti commerciali ottenibili (diodi, transistor, MOSFET, ecc.)

Caratteristiche del silicio prodotto:

- assoluta perfezione reticolare;

- materiale monocristallino fino a cilindri di massa di qualche quintale;

- livelli di impurezze al di sotto delle ppb (parti per miliardo; ossia μg/kg)

Produzione del Si purissimo Impurezze < 1 ppb

Crescita del monocristallo e preparazione dei wafer

Tecnologia planare sui wafer

Metallizzazione e assemblaggio

### 1. PURIFICAZIONE DEL SILICIO

Nel primo stadio della tecnologia del silicio, dalle materie prime del silicio (minerali a base di quarzo SiO<sub>2</sub>) mediante più passaggi si ottiene un silicio purissimo (11 nove: 99.99999999 %) con impurezze presenti minori di 1 ppb

#### 1. PURIFICAZIONE DEL SILICIO

Riduzione di SiO<sub>2</sub> a Si (met)

Formazione di SiHCl<sub>3</sub> da Si

Distillazione frazionata di SiHCl<sub>3</sub>

Deposizione di Si da SiHCl<sub>3</sub>

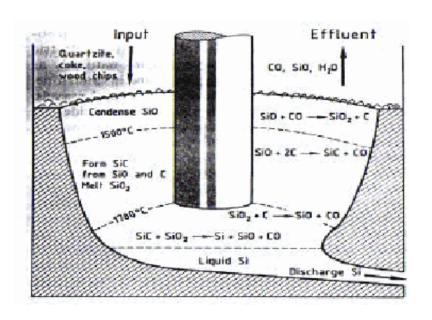

### 1a. RIDUZIONE DELLA SILIC

Riduzione della silice a silicio metallico in forno ad alta temperatura (1450 °C) in atmosfera riducente a contatto con carbone

$$SiO_2(s) + C(s) \rightarrow Si(l) + 2CO(g)$$

### 1a. RIDUZIONE DELLA SILICI

Il silicio così ottenuto è detto di "grado metallurgico" (98%) che viene purificato attraverso la trasformazione del silicio e delle impurezze in cloruri e successiva distillazione.

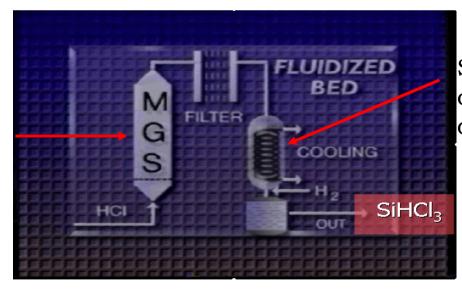

### 1b. FORMAZIONE DI SiHCl<sub>3</sub>

Trattamento a 300 °C in atmosfera di HCl in presenza di catalizzatori:

$$Si(s) + 3HCl(g) \rightarrow SiHCl_3(g) + H_2(g)$$

Reattore a letto fluido in cui reagisce il silicio ridotto in polvere

Settore di condensazione dei cloruri

## 1b. DISTILLAZIONE DI SiHCl<sub>3</sub>

Il triclorosilano è circa il 90 % del gas, mentre il residuo 10 % è dato da SiCl<sub>4</sub> e da cloruri di varie impurezze. La corrente gassosa è liquefatta (T < 31.8 °C) e quindi sottoposta a distillazione frazionata dalla quale si ottiene SiHCl<sub>3</sub> purissimo (le impurezze residue sono dell'ordine di 1 ppb)

ppb).

Colonne di distillazione

purissimo

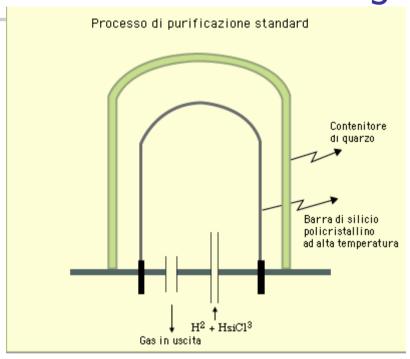

### 1c. DEPOSIZIONE DI Si DA SIHC

SiHCl<sub>3</sub> è gassificato e mescolato ad H<sub>2</sub> e quindi inviato nel reattore di riduzione dove avviene la preparazione del silicio policristallino purissimo:

$$SiHCl_3(g) + H_2(g) \rightarrow Si(s) + 3HCl(g)$$

ottenuta ad alta temperatura (1000-1100 °C) su una barra di silicio in atmosfera di H<sub>2</sub> e SiHCl<sub>3</sub>

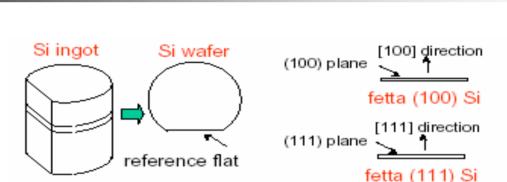

## 2. PREPARAZIONE DEI WAFER MONOCRISTALLINI

- Per controllare le caratteristiche elettriche dei dispositivi semiconduttori devono essere assenti il bordo e le dislocazioni.

- Il Si purissimo policristallino deve essere trasformato in Si monocristallino che è poi ridotto in fette ("wafer").

## 2. PREPARAZIONE DEI WAFE MONOCRISTALLINI

Crescita del lingotto Si monocr. Taglio del cilindro in "wafer" Trattamenti sul wafer Crescita epitassiale

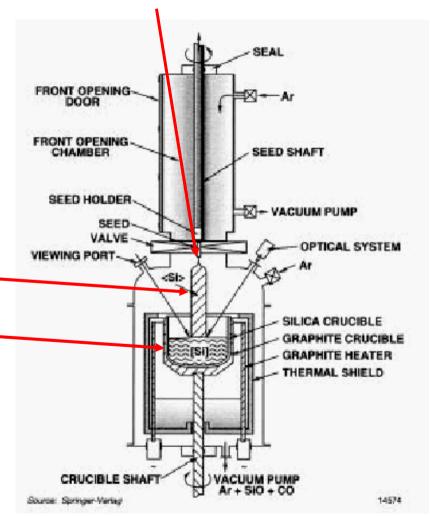

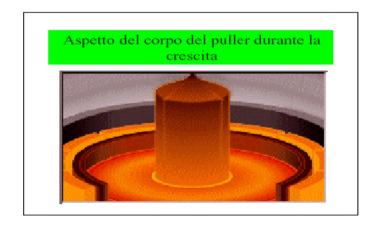

## 2a. CRESCITA DEL MONOCRISTALLO

Germe di Si iniziale

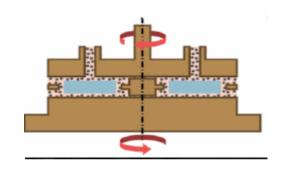

- Tecnica Czochralski (1917!)

- T = 1420 °C

- Lentissima velocità di avanzamento

Monocristallo di silicio

Recipiente con il silicio fuso assieme a eventuali droganti

## 2a. CRESCITA DEL MONOCRISTALLO

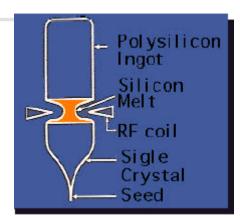

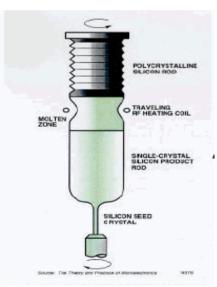

## 2a. CRESCITA DEL MONOCRISTALLO PER "FLOATING ZONE"

- Tecnica meno usata della precedente.

- Il policristallo è fuso in zone variabili con accumulo delle impurezze nella zona fusa.

- Purificazione e crescita del monocristallo contemporanea.

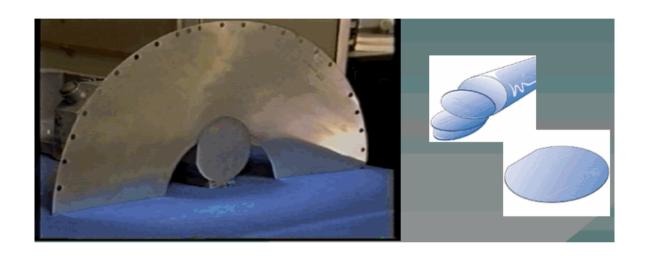

## 2b. TAGLIO DEL CILINDRO IN WAFER

- Il taglio viene fatto con seghe circolari o seghe a filo.

- I wafer così ottenuti devono essere accuratamente trattati su una superficie in modo da averla perfetta. Possono essere necessari dei trattamenti finali di crescita epitassiale per migliorare la perfezione della superficie.

- Sulla superficie ottenuta per questa via verranno costruiti i dispositivi elettronici desiderati.

## 2b. TAGLIO DEL CILINDRO IN WAFER

Le fette hanno spessore di circa 1 mm.

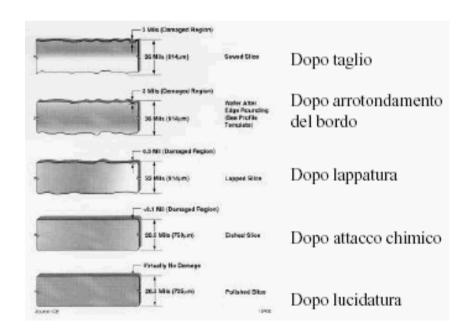

## 2c. TRATTAMENTI DOPO IL TAGLIO

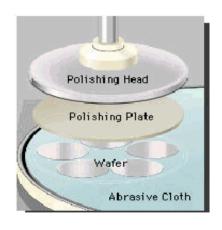

- Lappatura della superficie;

- Attacco chimico con HNO<sub>3</sub> e HF;

- Lucidatura finale

### 2d. CRESCITA EPITASSIALE

- La superficie può essere ulteriormente migliorata con processi di crescita epitassiale (molto costosi).

- Processo tipico è CVD (chemical vapor deposition). Gli atomi sono inviati nel reattore in composti gassosi che si riducono sulla superficie del wafer. Per il silicio la sorgente è il tetracloruro SiCl<sub>4</sub> che sulla superficie del wafer reagisce:

$$SiCl_4(g) + 2H_2(g) \rightarrow Si(s) + 4HCl$$

Per P la sorgente è la fosfina PH<sub>3</sub>, per il B è il diborano B<sub>2</sub>H<sub>6</sub>. Fosfina e diborano sono estremamente tossici; ci sono severe norme di sicurezza.

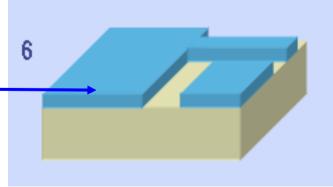

### 3. TECNOLOGIA PLANARE

- La tecnologia planare è basate sulle caratteristiche di SiO<sub>2</sub>, (effetto barriera, eccellente dielettrico e attacco selettivo con HF).

- Realizzazione dei dispositivi accedendo solo ad un piano del wafer (costruzione dall'alto).

- Grandissima miniaturizzazione dei dispositivi;

VLSI.

### 3. TECNOLOGIA PLANARE

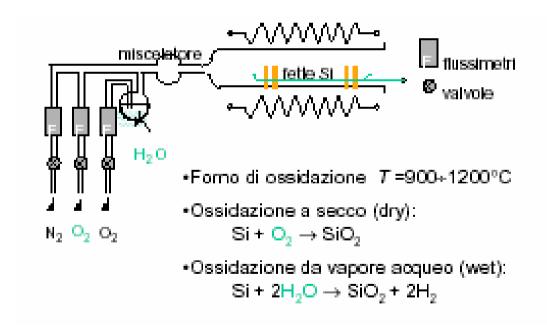

Ossidazione superficiale

Progettazione al computer del dispositivo

Fotolitografia per trasferire la geometria sul wafer

Drogaggio del wafer

### 3a. OSSIDAZIONE DEL WAFE

Processo di ossidazione termica in forno di quarzo dove Si in superficie è ossidato a SiO<sub>2</sub>.

È possibile determinare lo spessore di ossido in funzione del tempo.

## 3b. PROGETTAZIONE AL COMPUTER DEL DISPOSITIVO

Lo schema della disposizione dei vari componenti il dispositivo da realizzare (transistor, MOS, MOSFET, CMOS, ecc.) viene fatta con software opportuni (tipo CAD) in modo da minimizzare lo spazio necessario.

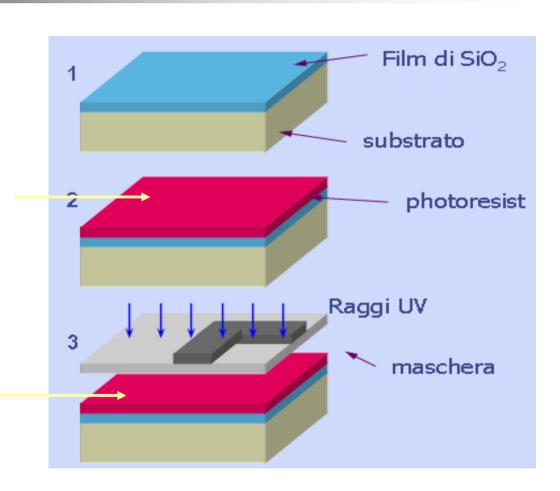

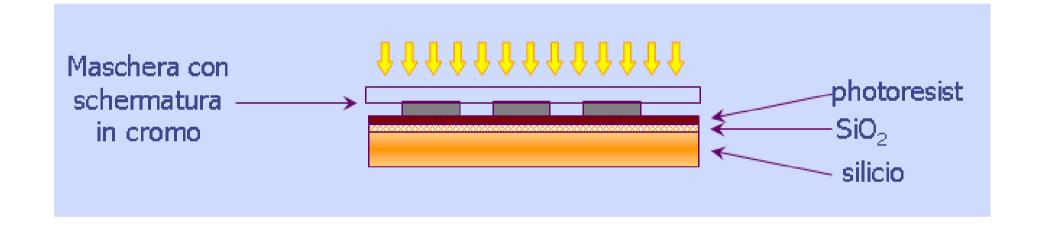

- Processo più delicato, critico e complesso nella fabbricazione dei circuiti microelettronici.

- Trasferimento della geometria progettata al CAD sul dispositivo.

- Preparazione di maschere opportune per "costruire" la necessaria microstruttura sul wafer attraverso opportuni trattamenti.

- La fotolitografia consiste sostanzialmente dei seguenti step (molte varianti sono possibili):

- a) deposizione di resist chimicamente fotosensibile;

- esposizione a raggi UV della superficie opportunamente mascherata;

- sviluppo del resist esposto ai raggi UV;

- attacco chimico selettivo.

Deposizione del photoresist

Applicazione della maschera ed esposizione ai raggi UV

## 3c. FOTOLITOGRAFIA: SCHERMATURA ED ESPOSIZIONE AI RAGGI UV

HF

5

$SiO_2(s) + 4HF(g) \rightarrow SiF_4(g) + 2H_2O(g)$

Rimozione del photoresist - polimerizzato e wafer pronto per il drogaggio

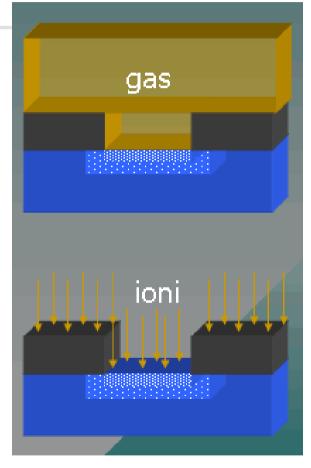

3d. DROGAGGIO DEL WAFER

- Due tecniche distinte disponibili:

- Diffusione ad elevata temperatura;

- Impiantazione ionica.