## Università degli Studi di Cassino

Corso di Calcolatori Elettronici I

Elementí di memoria e registri

Anno Accademico 2007/2008 Francesco Tortorella

#### Elementi di memoria

Nella realizzazione di un sistema digitale è necessario utilizzare degli elementi di memoria per:

- memorizzazione di dati (registri per istruzioni/dati, buffers, control/status, flag)

- sincronizzazione tra dati

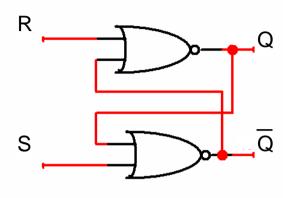

### Elementi di memoria: RS-latch

| S | R | Q   | Q   |

|---|---|-----|-----|

| 0 | 0 | 0/1 | 1/0 |

| 0 | 1 | 0   | 1   |

| 1 | 0 | 1   | 0   |

| 1 | 1 |     |     |

Calcolatorí Elettronicí I Lezione 11 - 2/19

#### Elementi di memoria: D-latch

Un D-latch è un elemento che permette la memorizzazione di un valore binario. Ha due ingressi:

•D (Data): il valore da memorizzare

•C (Clock): un segnale di abilitazione alla lettura

In uscita presenta il valore memorizzato Q ed il suo complemento Q

| С | D | Q   | Q   |   | II D lotob può cocoro                                |  |  |

|---|---|-----|-----|---|------------------------------------------------------|--|--|

| 0 | 0 | 0/1 | 1/0 |   | Il D-latch può essere realizzato tramite un RS-latch |  |  |

| 0 | 1 | 0/1 | 1/0 |   |                                                      |  |  |

| 1 | 0 | 0   | 1   |   |                                                      |  |  |

| 1 | 1 | 1   | 0   |   |                                                      |  |  |

|   |   |     |     |   | C                                                    |  |  |

|   | С | D   | R   | S |                                                      |  |  |

|   | 0 | 0   | 0   | 0 |                                                      |  |  |

|   | 0 | 1   | 0   | 0 |                                                      |  |  |

|   | 1 | 0   | 1   | 0 |                                                      |  |  |

|   | 1 | 1   | 0   | 1 |                                                      |  |  |

Calcolatorí Elettronicí I Lezione 11 - 3/19

F. Tortorella © 2008 Università degli Studi di Cassino

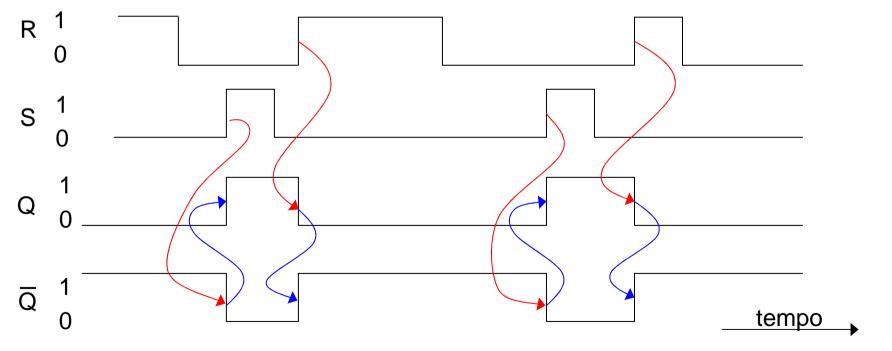

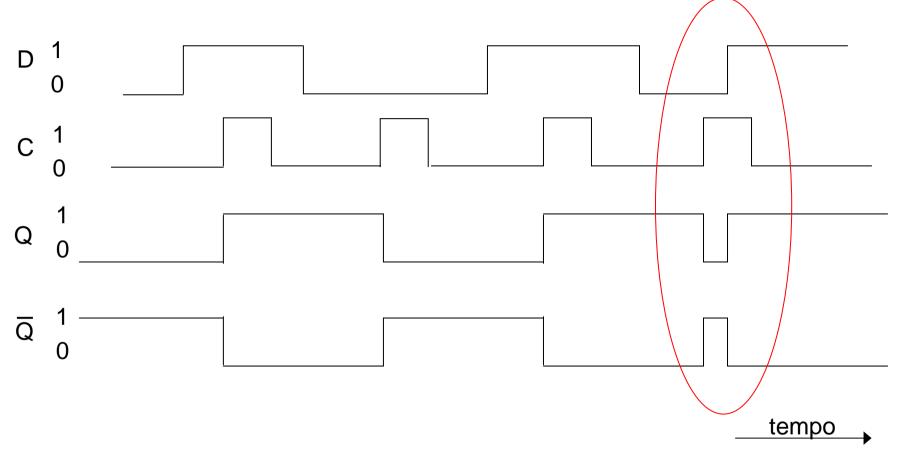

#### Andamento temporale del D-latch

Eventuali variazioni di D mentre C è alto vengono seguite

Calcolatori Elettronici I Lezione 11 - 4/19

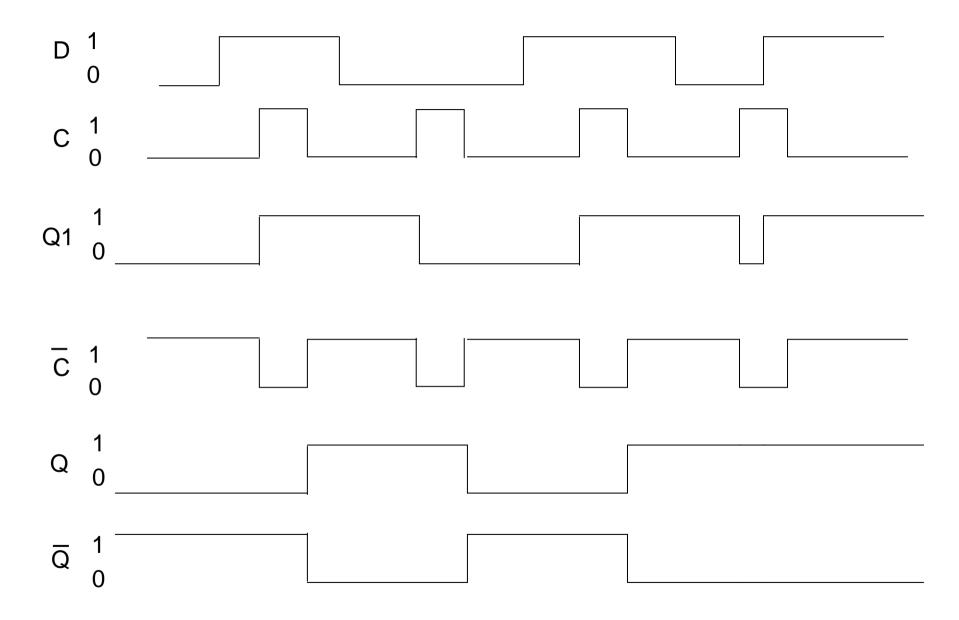

#### Elementi di memoria: flip flop D edge triggered

Gli elementi di memoria edge-triggered modificano il loro stato in corrispondenza del fronte di salita o di discesa del clock. In tal modo si evitano i problemi dei latch.

# Realizzazione Master-Slave D Q1 D Q2 Q C Q1 C Q2 Q

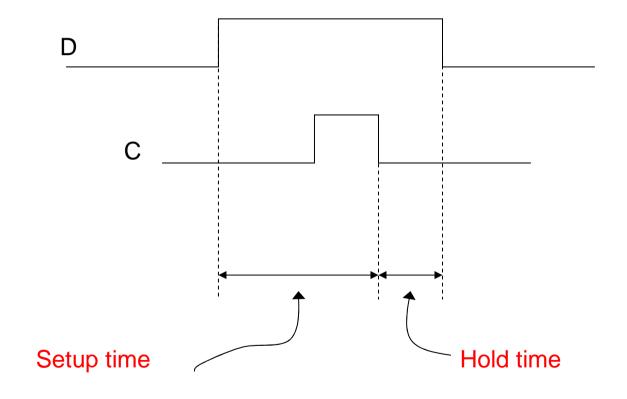

L'ingresso D deve essere stabile in un intervallo di tempo intorno al fronte del segnale C, altrimenti l'uscita del flip flop non è affidabile

Sono quindi definiti dei tempi minimi di durata del segnale D prima del fronte (setup time) e dopo il fronte (hold time)

Calcolatori Elettronici I Lezione 11 - 7/19

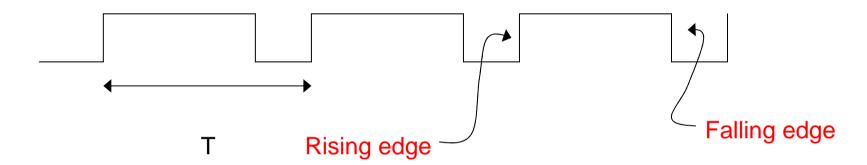

#### Clock

Il clock è un segnale periodico, definito da una propria frequenza f=1/T

Può assumere solo due valori (clock alto o clock basso). La transizione tra un valore ed un altro definisce un fronte di salita (*rising edge*) o di discesa (*falling edge*).

In un sistema digitale *sincrono* il segnale di clock viene utilizzato per determinare i cambiamenti di stato negli elementi di memoria.

Quando ciò avviene in corrispondenza di un fronte si parla di sincronizzazione edge triggered (edge triggered clocking)

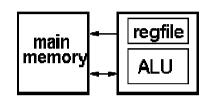

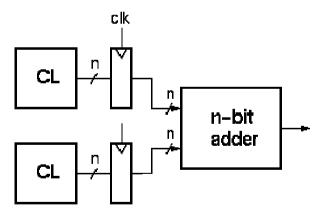

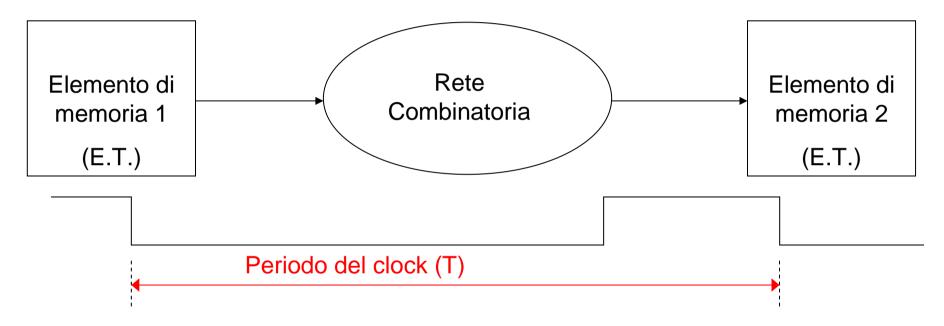

#### Il Clock in un sistema digitale sequenziale (1)

I segnali che sono ingresso di elementi di memoria devono essere stabili quando si verifica il fronte del clock.

Per assicurare la stabilità dei valori letti all'uscita della rete combinatoria, il periodo del clock deve essere sufficientemente lungo. Se  $t_d$  è il ritardo legato al percorso critico della rete combinatoria, allora T>  $t_d$ .

#### Il Clock in un sistema digitale sequenziale (2)

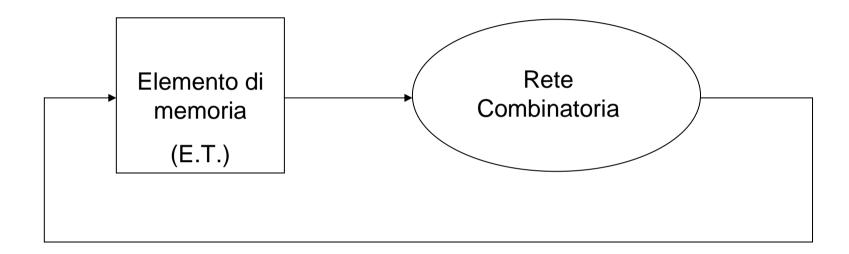

Con una sincronizzazione di tipo edge triggered è possibile realizzare delle retroazioni sugli stessi elementi di memoria.

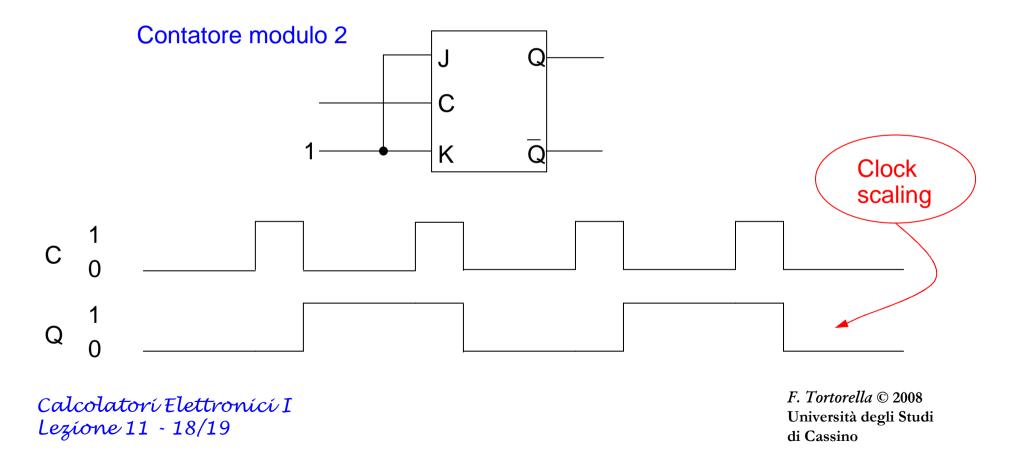

#### Elementi di memoria: flip flop JK

Il flip flop JK coincide con il flip flop RS tranne che per la combinazione J=K=1, in cui lo stato prossimo è definito come il complemento dello stato presente (contatore modulo 2).

| J | K | $Q_{n+1}$        |

|---|---|------------------|

| 0 | 0 | $Q_n$            |

| 0 | 1 | 0                |

| 1 | 0 | 1                |

| 1 | 1 | $\overline{Q}_n$ |

La retroazione diretta delle uscite non è realizzabile perché potrebbe condurre ad uno stato diverso da quello previsto o indurre un processo di oscillazione (se J=K=1).

Per avere una realizzazione efficiente è necessario separare logicamente le uscite correnti dagli ingressi. Soluzione ?

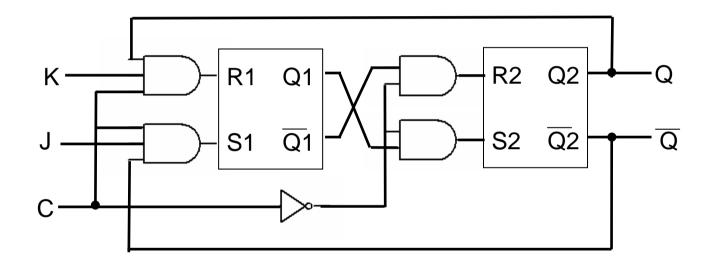

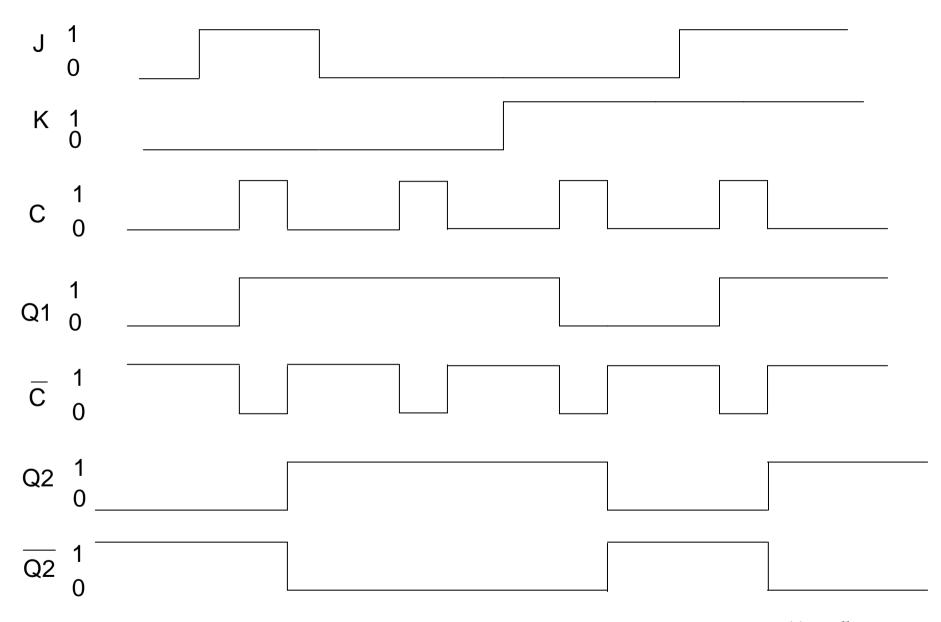

#### Realizzazione di flip flop JK

Una possibile realizzazione si ottiene tramite uno schema master-slave con bistabili RS abilitati.

Il primo stadio separa logicamente le uscite correnti (Q2,Q2) dagli ingressi (R2,S2) dello stadio finale che opera la commutazione dello stato dell'intero flip flop.

Calcolatorí Elettronicí I Lezione 11 - 13/19

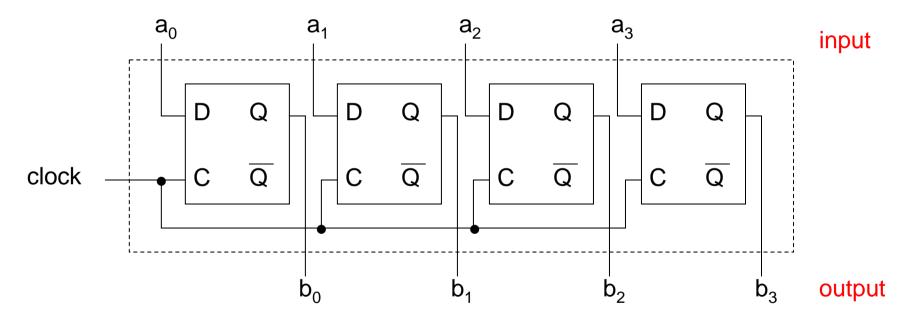

#### Registri

Un singolo bistabile è sufficiente per memorizzare un bit. Per memorizzare dati rappresentati su più bit è conveniente organizzare più bistabili in una struttura comune, il *registro*.

I bistabili sono sincronizzati da un clock comune in modo da caricare (o leggere) i dati in tutti i bistabili contemporaneamente.

#### Registri a scorrimento (1)

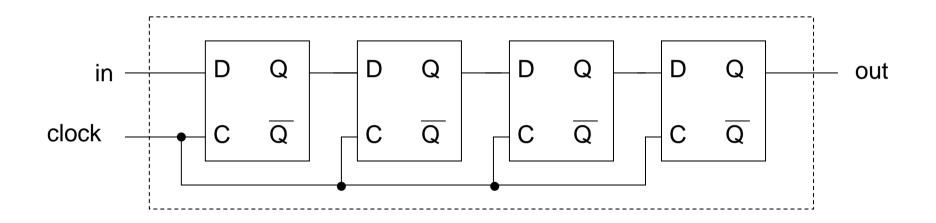

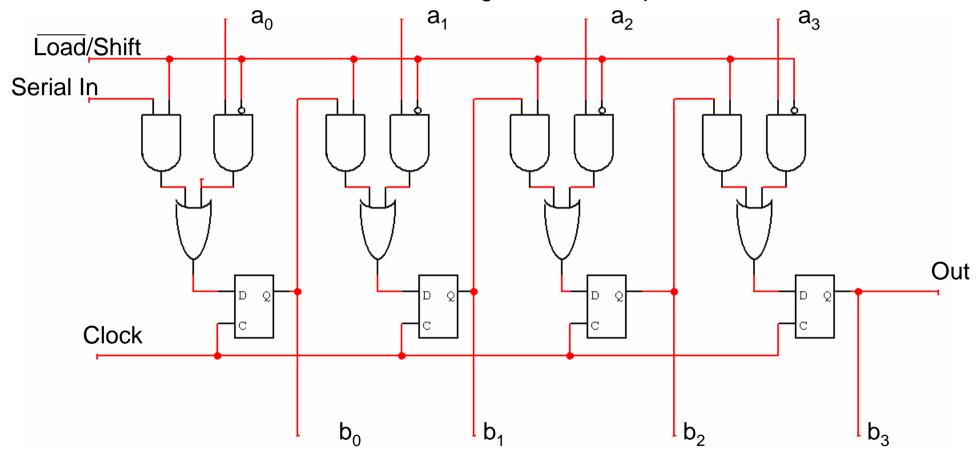

In diversi tipi di elaborazioni è necessario operare delle traslazioni (shift) o delle rotazioni sui contenuti di una registro. Un supporto hardware che rende possibile questa operazione è fornito dal registro a scorrimento (shift register).

Ad ogni impulso di clock il contenuto del registro trasla di una posizione verso destra.

Quali sono i vincoli sulla tempificazione dei bistabili?

#### Registri a scorrimento (2)

Un tipo particolarmente utile di registro a scorrimento è quello che consente la scrittura e la lettura del contenuto del registro anche in parallelo.

Calcolatorí Elettronicí I Lezione 11 - 16/19

F. Tortorella © 2008 Università degli Studi di Cassino

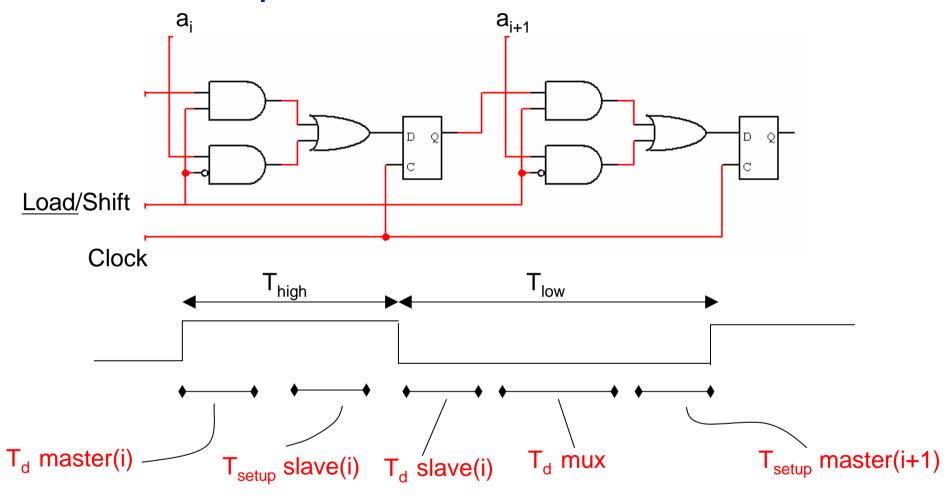

#### Definizione del periodo di clock

$T_{high} > T_{d}master(i) + T_{setup}slave(i)$

$T_{low} > T_{d}slave(i)+T_{d}mux+T_{setup}master(i+1)$

Calcolatorí Elettronicí I Lezione 11 - 17/19

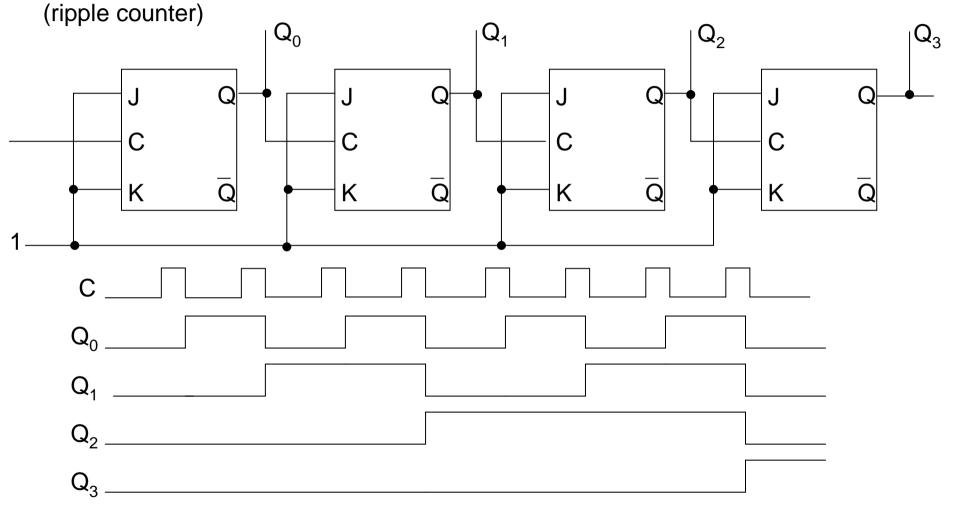

#### Contatori (1)

Circuiti fondamentali nella realizzazione di sistemi di elaborazione.

Forniscono, in maniera codificata, il numero delle volte che si è verificato un evento (es. falling edge di un segnale in ingresso).

Il conteggio avviene mod 2k, se l'uscita è su k bit.

#### Contatori (2)

Contatore mod 2<sup>k</sup> realizzato tramite k contatori mod 2 montati in cascata